A blog to explore whole VLSI Design, focused on ASIC Design flow, Physical Design, Signoff, Standard cells, Files system in VLSI industry, EDA tools, VLSI Interview guidance, Linux and Scripting, Insight of Semiconductor Industry and many more. Happy learning!

21 June

Crosstalk Timing Window Analysis and Prevention Techniques

17 June

Crosstalk Noise and Crosstalk Delay - Effects of Crosstalk

In the previous article, we have discussed signal integrity, crosstalk, crosstalk mechanisms and the parasitic capacitances associated to interconnects. In this article, we will discuss the effects of crosstalk. Crosstalk has two major effects:

- Crosstalk glitch or crosstalk noise

- Crosstalk delta delay or crosstalk delay

Crosstalk glitch

In order to explain the crosstalk glitch, we will consider the following two cases. There might be many more similar cases.

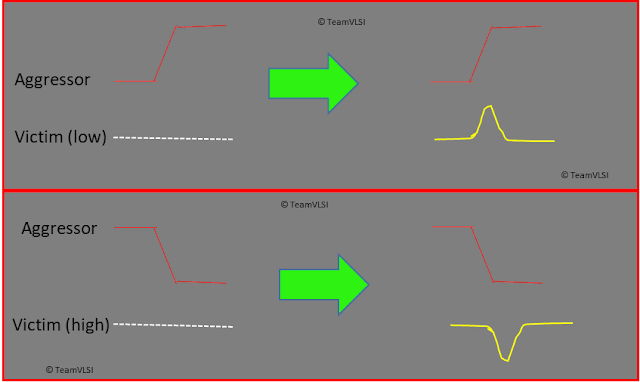

Case-1: Aggressor net is switching low to high and victim net is at a constant low

Figure-1: Crosstalk glitch (Raise)

In this case, the aggressor net switches from logic 0 to logic 1 and victim net is at constant zero as shown in the figure-1. Now consider the node A, node V, Mutual capacitance Cm and path from A to V. As node A start switching from low to high, a potential difference across the mutual capacitance get developed and the mutual capacitor Cm starts charging. During this event, there is some leakage current which starts flowing from node A to node V through the mutual capacitance Cm due to the leaky nature of mutual capacitance. This leakage current will raise the potential of node V, which creates a raising spike or raising glitch on the victim net as shown in figure-1. The magnitude of this voltage or height of glitch will depend on the various factors which will be discussed later.

So, whenever one net switches from low to high and other neighbouring net is supposed to remain constantly low, will get affected by the switching net and have a glitch on it. Now let's discuss the case-2 which is similar to the case-1.

Case-2: Aggressor net is switching high to low and victim net is at a constant high

|

| Figure-2: Crosstalk glitch (Fall) |

In this case, the aggressor net switches from logic 1 to logic 0 and victim net is at constant high logic as shown in the figure-2. Now consider the node A, node V, Mutual capacitance Cm and path from V to A. As node A start switching from high to low, a potential difference across the mutual capacitance gets developed and the mutual capacitor Cm starts charging through node V to node A. During this event, there is a leakage current which starts flowing from node V to node A through the mutual capacitance Cm due to the leaky nature of mutual capacitance. This leakage current will drop the potential of node V, which creates a falling spike or falling glitch on the victim net as shown in figure-2.

So, whenever one net switches from high to low and other neighbouring net is supposed to remain constantly high, will get affected by the switching net due to the mutual capacitance and have a falling glitch on it.

In case-1 and case-2 we have seen that if one net is switching and another neighbouring net is at constant logic and if they have mutual capacitance between them, the other net may get affected and that net may have a sudden raising or falling bump or spike. such a spike on victim net is called crosstalk glitch or crosstalk noise. Figure-3 shows the situations when there is a raise glitch or fall glitch.

|

| Figure-3: Raising and Falling glitch in crosstalk |

Effects of crosstalk glitch

Does every glitch unsafe? The answer is it depends on the height of glitch and the logical connection of the victim net. If the height of glitch is within the noise margin low (NML), Such a glitch is considered as a safe glitch. If the glitch height is above the noise margin high (NMH), such a glitch is considered as a potentially unsafe glitch. In the case of glitch height is in between NMH and NML, this is an unpredictable case. Figure-4 shows the CMOS inverter transfer characteristics and Noise margins.

|

| Figure-4: CMOS transfer characteristics and Noise margin |

As the technology node shrinks, the supply voltage also gets lowered down. In lower supply voltage, noise margin will be lesser. If noise margin is lesser it is more prone to have a potentially unsafe glitch. Figure-5 will help to understand this fact.

|

| Figure-5: Safe and unsafe glitch based on glitch heights |

Figure-5 shows safe and unsafe glitch based on glitch heights. Safe glitch has no effect on the next logic of the victim net and the logic of the victim net will be treated as correct logic. But in other cases, the victim net's logic may be treated as wrong logic due to the glitch and a wrong data will be propagated which might cause the failure of chip. Generally reset pins of memory is a constant logic and if such pin's net has an unsafe crosstalk glitch, memory might get reset. Many other situations may occur which may cause chip failure due to the unsafe glitch.

But there are some cases where there are no effects of crosstalk glitches. For example, consider there is a two-input AND gate whose one input is tied at constant 0 and at the other input nets there is crosstalk happening. so whatever the effects of crosstalk, the output always will be Zero. similar cases are for many combinational logic where there would be no effects of crosstalk. Again in case of glitch height is within the range of noise margin low.

Crosstalk glitch height

Crosstalk glitch will be safe or unsafe depends on the height of crosstalk glitch and the logic pin from which the victim net is connected. So let's investigate the factors on which the crosstalk glitch height depends.

Crosstalk glitch height depends basically on three factors:

Coupling capacitance

Aggressor's drive strength

Victim's drive strength

Coupling capacitance

Aggressor's drive strength

Victim's drive strength

Closer the nets will have greater coupling capacitance. More the capacitance will have larger glitch height. Drive strength of the aggressor and victim driver will also affect the glitch height. The high drive strength of the aggressor net will impact more the victim net. If the drive strength of the victim net is high, then it will not be easy to change its value, that means lesser will be the effect of crosstalk.

It was all about the crosstalk glitch or crosstalk noise, Now let's move the second effects which is crosstalk delta delay or crosstalk delay.

Crosstalk Delay

Crosstalk delay occurs when both aggressor and victim nets switch together. It has effects on the setup and hold timing of the design. Crosstalk delay may cause setup and hold timing violation. So it is important to do crosstalk delay analysis and fix the timing considering the effect of crosstalk.

Case-3: Aggressor and victim net switch in opposite directions

Case-4: Aggressor and victim nets switch in the same direction

Effects of crosstalk delay

|

| Figure-10: Effect of crosstalk delay on clock tree |

|

| Figure-11: Effect of crosstalk delay on setup timing |

|

| Figure-12: Effect of crosstalk delay on hold timing |

Signal Integrity and Crosstalk effect in VLSI

“According to a research conducted by Collett International Research Inc., one in five chips fails because of the signal integrity.”

In this article, we will discuss a very important issue of VLSI design called signal integrity and crosstalk which are responsible for the failure of many ASICs now a day. We will discuss signal integrity and crosstalk in this article. The effects of crosstalk and prevention techniques will be discussed in the next two articles.

Signal Integrity:

Signal could be defined as information in the form of wave/impulse which is used for communication between two points. In Digital form, it is either in state 1 (high) or in state 0 ( Low) as shown in the figure-1 below.

By definition integrity means “complete or unimpaired”. Or We can say that maintaining the actual form of anything over time without any distortion.

So signal

Integrity could be defined as replication of the entire signal while transmitting

from one point to another without any distortion in its quality.

Or In a broader perspective,

we can

say that

Signal Integrity is the ability of an electrical signal to carry information

reliably and resist the effects of high-frequency electromagnetic interference

from nearby signals.

Signal

Integrity addresses two concerns in digital design

•Timing

of signal – Does the signal reach the destination when it is supposed to?

•Quality

of signal – When the signal reaches, is it in good condition?

“Timing”

is everything in high-speed digital design.

“Timing” is everything in high-speed digital design.

So the goal of Signal Integrity is to ensure reliable, high-speed data transmission from one point to another point inside the chip through the metal lines. Increased data rate and lower technology node, Maintaining signal integrity is a big challenge.

In a nutshell, if the signal travels through a net without any distortion, Signal Integrity is high, If there are lots of noise added on it / distortion occur/delay occurred, Signal Integrity is less.

Signal Integrity may be affected by various reasons, but major reasons are:

In next section we will discuss Crosstalk issue.

What is Crosstalk?

Crosstalk could be defined as a phenomenon in which logic transmitted in one net creates undesired effects on its neighbouring nets. Or in another world, we can say switching of a signal in one net can interfere in the neighbouring net, which is called crosstalk.

When a signal switches, it may affect the voltage waveform of a neighbouring net. The switching net is typically identified as the “aggressor” and the affected net is the “victim.” Figure-2 shows a typical arrangement of aggressor and victim net.

|

| Figure-2: Aggressor and Victim nets |

Crosstalk is a very severe effect especially in lower technology node and high-speed circuits and it could be one of the main reason of chip failure. In the next section, we would discuss the crosstalk mechanism in VLSI Design.

Crosstalk mechanism

Crosstalk occurs via two mechanisms:

- Inductive Crosstalk

- Electrostatic crosstalk

Electrostatic crosstalk occurs due to mutual capacitance between two nets. The electric voltage in a net creates an electric field around it. If the electric field is changing, It can either radiate the Radio waves or can couple capacitively to the adjacent net. Such coupling of the electric field is called electrostatic crosstalk.

Out of two mechanisms explained here, Electrostatic Crosstalk mechanism is more significant and problematic than Inductive crosstalk. So in this section, we will talk about Electrostatic crosstalk.

Parasitic capacitances related to Interconnects

The main reason of crosstalk is the capacitance between the interconnects. So in this section, we will investigate various capacitance associated with metal interconnects. Figure-3 shows the various parasitic capacitances get formed inside an ASIC (click on image for a better view).

|

| Figure-3: Various capacitances associated with interconnects |

After the FEOL (Front Line Of Line) fabrication, a thick SiO2 insulating layer is deposited all over the substrate before metal-1 (M1) layer fabrication. The insulating layer between M1 and substrate acts as a dielectric and forms a capacitance between M1 and substrate. this is called substrate capacitance (cs). M1 is patterned and the unwanted metal areas are etched away and again empty regions are filled with SiO2. So there is the formation of parasitic capacitance between two neighbouring M1 nets (same metal layers) which is called lateral capacitance (CL). M2 layer is fabricated above M1 followed by SiO2 layer. So there is the formation of interlayer capacitance (CI) between any two conjugative metal layers. Interlayer capacitance can be formed not only conjugative metals but also the metals far away to each other, like M2-M4 or M2-M5. The value of all these capacitance depends on two factors, common area and the gap between them. These capacitances are directly proportional to the common area between them and inversely proportional to the gap between them.

Summary

This article explained the signal integrity, crosstalk, crosstalk mechanisms and parasitic capacitances related to interconnects. The effects of crosstalk are crosstalk glitch or crosstalk noise and crosstalk delay or delta delay. In the next article, we will discuss crosstalk glitch and crosstalk delay.

Thank you.

14 June

Antenna Prevention Techniques in VLSI Design

In the last article, we have discussed the antenna violation. How antenna violations occur, what is the mechanism to occur antenna effect or Plasma Induced Gate oxide damage. So in this article, we will discuss the solution part of the antenna effect, that is how to prevent the antenna violations.

How to prevent antenna violation?

Before discussing the prevention, let's recall the root cause of the antenna effect, then it will be easy to understand the prevention techniques. Antenna effect occurs mainly due to the excessive accumulation of charges on a metal interconnect connected to the gate of transistors during the plasma etching of metal interconnect. The amount of accumulated charge depends on the area of the metal interconnect connected to the gate. The excessive accumulated charges get discharged through the thin gate oxide and it causes permanent damage in the gate oxide.

- Metal hopping

- Floating gate attachment

- Antenna diode

Antenna Rules

- Antenna ratio is the ratio of the metal area connected to the gate to the total area of the gate

- Antenna ratio is defined in the following form:

Example of antenna rule violation

Total gate area = 0.6 x 2 = 1.2um^2

Total gate area = 0.6 x 2 x 4= 4.8um^2

Total gate area = 0.6 x 2 = 1.2 um^2

How to fix the antenna violations

- Reduce the antenna area - Jumper insertion or metal hoping

- Increase the gate area - by dummy transistor insertion

Antenna Checks (Physical Verification)

- Antenna checks verify the layout against the antenna rules of rule decks. There are many more checks need to perform before tapeout like DRC, ERC, LVS etc and these all are collectively called physical verification of layout.

- Physical verification tools (like Calibre, Assura, IC Validator) varifies the antenna rule for all the layers for which antenna rule is applicable.

- Antenna rules strongly depend on the process nodes.