Code: INTL0Y032021DFT

This interview was held for the position of DFT Engineer with 0 years of experience. I personally felt the questions are good and generic which will help the freshers in other domains too.

Round-1:

1) Differences between MOSFET and FINFET ?

2) Puzzle: A blind man walking in a desert has 2 red pills and 2 blue pills with him. He has to take one red pill and one blue pill each per day. How can he do that correctly?

3) Limitations of MOSFET

4) Puzzle: If a man climbs 15 m well. He climbs 4 m every day and slips 3 m . How many days it takes for him to get outside of the well?

5) What is set up time and hold time?

6) What is set up time and hold time violations?

7) What is metastability and do you know its physical significance?

8) What is a critical path?

9) How can you improve the timing?

10) How can you fix the setup time violations?

11) Implement a 2:1 mux for AND gate?

12) Draw the timing diagram of half adder?

13) What is blocking and non-blocking assignments?

14) What is synchronous and Asynchronous reset?

15) Why do we need DFT and what do you mean by that ?

16) Explain briefly the methods of DFT?

17) Why do you need to make flip flops initialized in an ad hoc technique?

18) What are controllability and observability?

19) If you fabricate a full adder and do the functional test and verify outputs are correct, then do you still require DFT also?

20) What is BIST?

21) What is JTAG?

22) Difference between verification and DFT?

23) What is yield?

24) Explain your course works and the projects.

25) Difference between RAM, ROM.

26) What is DMA?

1) Short channel effects in MOSFET.

2) Brief about JTAG.

3) Any insight into BSDL.

4) What are the different faults that occur while fabrication?

5) What is bridging fault?

6) What is fault collapsing?

7) Draw a D-flipflop along with a timing diagram.

8) What is Stuck at faults?

9) What do you mean by clock skew?

10) Is Hold time dependent on clock frequency?

11) Is clock skew an advantage or not?

12) Current technology node used in industry?

13) Is set up time-dependent on clock frequency?

14) Why do you need a reset in flip flop?

15) What is the multicycle path?

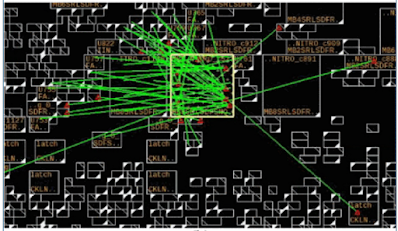

16) Any tools for DFT?